# Steady-State Analysis of a ZVS Bidirectional Isolated Three-Phase DC–DC Converter Using Dual Phase-Shift Control With Variable Duty Cycle

Herminio Miguel de Oliveira Filho, Student Member, IEEE, Demercil de Souza Oliveira Jr., Senior Member, IEEE, and Paulo Peixoto Praça, Member, IEEE

Abstract—This study presents the steady-state analysis and experimental results on a soft-switching bidirectional isolated threephase dc-dc converter using DPS control with variable duty cycle. The topology uses three single H-bridges in the primary side and a three-phase inverter in the secondary side. High-frequency isolation is ensured by using three single-phase transformers connected in open delta-wye configuration. The variation of both phase-shift angles between the H-bridge legs and/or primary and secondary sides allows controlling the power flow, while reduced reactive power flow is possible. The variable duty cycle is used to ensure a constant voltage bus and/or zero voltage switching operation. A detailed analysis is presented considering a model based on the fundamental components for the voltages and currents in the transformer. A comparison between the fundamental and the actual models is carried out to validate the proposed model. Experimental results on a 96 V/350-400 V, 3.5 kW prototype are presented and discussed to validate the proposed approach.

*Index Terms*—Bidirectional power flow, dual phase-shift control, phase-shift (PS), soft-switching, three-phase dc–dc converter.

#### I. INTRODUCTION

**R** ESEARCH works regarding dc–dc converters have substantially increased in the last few years due to applications in hybrid electric vehicles, standalone renewable energy systems, dc distribution, smart-grids, and solid-state transformers. One of the most popular topologies is the zero voltage switching, phase-shift, pulse width modulation (ZVS-PS-PWM) full-bridge converter. However, the components may present appreciable stresses at high power levels [1].

Troubleshooting of the previous converter was presented in 1988 by Prasad [2], who introduced the "three-phase dc–dc conversion" concept that uses a three-phase inverter, a three-phase rectifier, and a high-frequency isolation transformer. Thus, it is possible to reduce the components stress and also the trans-

Manuscript received December 24, 2014; revised March 7, 2015; accepted April 14, 2015. Date of publication April 30, 2015; date of current version November 16, 2015. This work was supported by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) and Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq). Recommended for publication by Associate Editor H. Li

H. M. d. Oliveira Filho is with the Institute for Engineering and Sustainable Development (IEDS), University for the International Integration of the Afro-Brazilian Lusophony (UNILAB), Acarape 62785-000 Brazil (e-mail: herminio@unilab.edu.br).

D. d. S. Oliveira Jr. and P. P. Praça are with the Electrical Engineering Department, Federal University of Ceará (UFC), Fortaleza 60455-760 Brazil (e-mail: demercil@dee.ufc.br; paulopp@dee.ufc.br).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2015.2428271

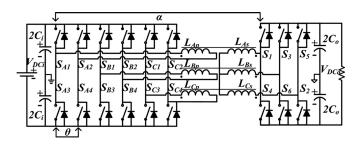

Fig. 1. Proposed topology.

former volume by increasing the current and voltage ripple frequency in both input and output sides. Three-phase dc–dc converters using the resonance concept were developed aiming to improve the performance of the converter presented in [2], e.g., [3]–[5] and [6], where soft-switching is achieved at the cost of high voltage and current stresses. The converters presented in [1], [7], and [8] apply asymmetrical duty modulation to obtain soft-switching, while the rms current through the semiconductors is minimized if compared to resonant converters. The optimum characteristics of the three previous converters are obtained in [9] by applying PS modulation. Solutions using current-fed converters e.g., [10]–[12] and [13] were developed resulting in low input current ripple. Topologies with buck characteristics using three-level structures in the primary side were also proposed in [14]–[16] to achieve high voltage levels.

In 1991, De Donker [17] presented the first bidirectional three-phase dc–dc converter known as dual active bridge (DAB), which uses the leakage inductance and PS concept to control the power flow. Modulation [18] and control [19] techniques were performed to improve efficiency in the DAB converter. Other bidirectional solutions have been developed using PS, e.g., [20]–[22], and the use of resonant converters associated with the aforementioned technique is also possible [23]. The work described in [24] shows that the power flow is controlled by adequately driving the switches. Asymmetrical PWM dc–dc three-phase topology in [25] proposes a bidirectional version based on [1], but using a Y- $\Delta$  transformer to naturally double the conversion ratio.

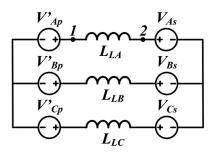

This study presents a bidirectional version of the topology introduced in [9] without output inductor filter, which is shown in Fig. 1. The converter allows increasing the involved power ratings by paralleling phases and not multiple devices. Besides, the turns ratio can be decreased in this case due to the double output voltage obtained by using an open delta-wye transformer,

0885-8993 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

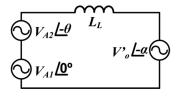

Fig. 2. Per-phase model of the dc-dc converter topology.

thus minimizing the effects of parasitic elements and improving the transformer performance. The possibility of direct and indirect power flow is achieved with DPS [26], [27]. Considering appropriate phase angles, it is possible to reduce the reactive content and also the transformer volume. The duty cycle of the input bridge in association with PS can be varied to regulate the input bus voltage [20], also ensuring ZVS over the entire load range [29].

Since there are three possible control variables, the operation of the proposed topology is very complex, as an alternative theoretical analysis first presented in [30] and [31] is developed considering a model based on fundamental components. Besides the detailed study, a comparison between the fundamental and actual models is carried out to validate proposed model, and experimental results are also presented and discussed in this paper.

#### II. ANALYSIS OF THE FUNDAMENTAL MODEL

Conceptually, each phase of the converter can be seen as an inductor  $L_{\rm L}$  (i.e., the transformer leakage inductance) connected at either terminal by a controlled square-wave voltage source. In order to simplify the analysis, the square-wave sources are replaced by their respective fundamental components and the output voltage is referred to the primary side. This model is identified as the synchronous-machine equivalent circuit and may present similar properties. Since all quantities are sinusoidal at a single frequency, a vector analysis can be carried out [17]. The per-phase model of the proposed topology is presented in Fig. 2 and DPS strategy is developed to control the power flow and provide the proper operation of the converter. The voltage sources use control angles  $\alpha$  and  $\theta$ , which correspond to the phase displacements of the secondary bridge and the primary bridge leg A2 with regard to the primary bridge leg A1, respectively.

#### A. Power Flow

Both the input voltage magnitudes  $V_{A1}$  and  $V_{A2}$  vary in magnitude and phase with the duty cycle d, according to (1) and (2). Upper input switch  $S_{A1}$  duty cycle is used as reference angle

$$V_{A1} = V_{A2} = V_i \left( d \right) \cdot e^{j\gamma} \tag{1}$$

$$\gamma = \pi \left( 0.5 - d \right) \tag{2}$$

where  $V_i(d)$  is obtained from the fundamental component of the leg with regard to the dc bus midpoint and  $\gamma$  is the displacement phase due to duty cycle variation.

The rms value of the fundamental component is obtained by applying Fourier series to the square-wave voltage as

$$V_i(d) = \frac{V_{\mathrm{dc}_i}}{2 \cdot \pi} \cdot \sqrt{\frac{v' + v''}{2 \cdot \pi}}$$

(3)

where

$$v' = 2\sin[2\pi(d+2)] - \sin[4\pi(d+1)]$$

(4)

$$v'' = 16 \cdot \pi \cdot \sin\left(\pi \cdot d\right) + \sin\left(4 \cdot \pi \cdot d\right) \tag{5}$$

Expression (3) can be used to determine the rms value of the fundamental output voltage, although  $V_{dco}$  must be referred to primary side using (6)

$$q = \frac{V_{\mathrm{dc}_o}}{V_{\mathrm{dc}_i}} = 4 \cdot n \cdot (1 - d) \tag{6}$$

where *n* is the transformer turns ratio. The output voltage magnitude is obtained fixing d = 0.5 and replacing the input voltage bus  $V_{dci}$  for the output voltage bus  $V_{dco}$  (as referred to primary side) in (3). Then, the following expression results:

$$V'_o = G \cdot 2 \cdot V_i (d) = G \cdot 2 \cdot V_i (0.5) = 2 \cdot G \cdot V_i$$

(7)

where G is the static gain between  $V_o$ ' and  $V_i$  and the term "2" that appears in expression (7) is due to open delta-wye connection. The current phasor representation in steady-state condition is given by

$$\hat{I}_L(\alpha, \theta, d) = \frac{V_{A1} \cdot e^{j0} - V_{A2} \cdot e^{-j\theta} - V'_o \cdot e^{-j\alpha}}{j \cdot 2 \cdot \pi \cdot f_s \cdot L_L}$$

(8)

where  $f_s$  is the switching frequency.

By substituting (1) and (7) into (8), the final expression for the current phasor is obtained as

$$\hat{I}_{L}\left(\alpha,\theta,d\right) = \frac{V_{i}\left(d\right) \cdot e^{j\gamma} \cdot \left(1 - e^{-j\theta}\right) - 2 \cdot G \cdot V_{i} \cdot e^{-j\alpha}}{j \cdot 2 \cdot \pi \cdot f_{s} \cdot L_{L}}.$$

(9)

The active and reactive powers are given by (10) and (11), respectively, and the base power is defined as (12)

$$P_o(\alpha, \theta, d) = \operatorname{Re}\left[\left(2 \cdot G \cdot V_i \cdot e^{-j\alpha}\right) \cdot \hat{I}_L^*(\alpha, \theta, d)\right]$$

(10)

$$Q_o(\alpha, \theta, d) = \operatorname{Im}\left[\left(2 \cdot G \cdot V_i \cdot e^{-j\alpha}\right) \cdot \hat{I}_L^*(\alpha, \theta, d)\right]$$

(11)

1 p.u. =

$$\frac{V_i (0.5)^2}{2 \cdot \pi \cdot f_s \cdot L_L}$$

. (12)

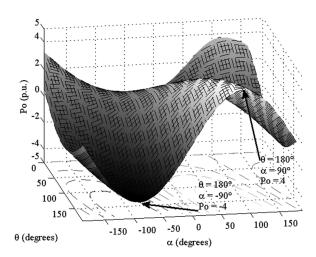

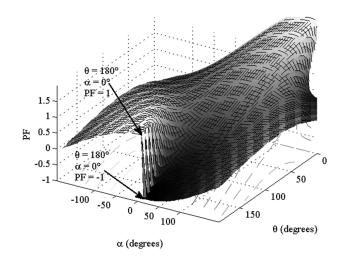

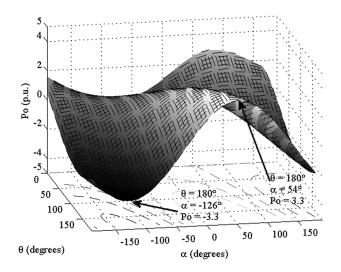

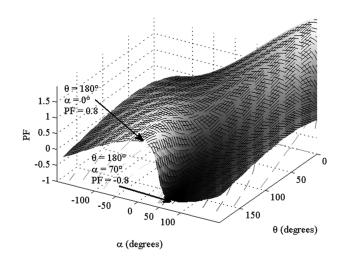

According to (10)–(12), the characteristics of the active power  $P_{\rm o}$  and power factor PF for the converter varying angles  $\theta$  and  $\alpha$  can be obtained according to Figs. 3 and 4, respectively, considering that the duty cycle is 0.5. The highest active power values occur when  $\theta$  and  $\alpha$  tend to 180° and 90°, respectively. Besides, the highest values for PF occur when  $\theta$  and  $\alpha$  tend to 180° and 0°, respectively, where  $P_{\rm o}$  is approximately null.

Fig. 5 shows the profile of  $P_0$  by varying angles  $\theta$  and  $\alpha$  for d = 0.3. By decreasing the duty cycle, the maximum values of  $P_0$  tend to occur at smaller values of  $\alpha$  if compared with the previous case. It can be seen that the maximum value of  $P_0$  is about 3.3, which is less than that obtained in Fig. 3, i.e., equal to 4. When the duty cycle is not equal to 0.5, the phase

Fig. 3. Active power (p.u.) for d = 0.5.

Fig. 4. Power factor for d = 0.5.

Fig. 5. Active power (p.u.) for d = 0.3.

Fig. 6. Power factor for d = 0.3.

current becomes asymmetrical, implying the increase of reactive power flow and the consequent reduction of the maximum active power. The power factor profile is shown in Fig. 6, as it can be observed that the maximum value is about 0.8. The maximum and minimum PF points are separated by values that vary decreasingly.

For cases where the duty cycle is higher than 0.5, i.e., d = 0.7, similar results to those for d = 0.3 are obtained, although  $P_0$  and PF vary in the reverse direction.

Therefore, it is possible to observe from the previous graphs that the effective PS between primary and secondary fundamental voltages  $\alpha$ ' can be controlled using three variables so that harmonics and reactive content can be optimized. For example, if  $\theta$  or *d* decrease, then  $\alpha$  needs to increase in order to ensure  $\alpha$ ' constant and to limit the reactive contents.

#### **B.** Switching Characteristics

The switching profile of the proposed converter is obtained from the time-varying analysis of the current

$$i_L(\omega \cdot t) = \sqrt{2} \cdot I_L(\alpha, \theta, d) \cdot \sin(\omega \cdot t - \varphi)$$

(13)

where  $\varphi$  is the lag angle with regard to the voltage defined as

$$\varphi = \arctan \frac{\operatorname{Im} \left[ \hat{I}_L \left( \alpha, \theta, d \right) \right]}{\operatorname{Re} \left[ \hat{I}_L \left( \alpha, \theta, d \right) \right]}.$$

(14)

The condition that allows achieving ZVS in the upper switch of the input bridges lies in defining  $i_L(0) = 0$ . Applying this condition to (13) gives

$$\sin\left(-\varphi\right) = 0\tag{15}$$

The static gain expression for the boundary curve between the soft and hard switching regions for the upper switch is obtained by substituting (14) into (15) and rearranging the resulting equation as

$$G_{iu} = \frac{V_i\left(d\right) \cdot \left[\cos\gamma \cdot \left(1 - \cos\theta\right)\right] + \sin\gamma \cdot \sin\theta}{2 \cdot V_i \cdot \cos\alpha}.$$

(16)

The active power for the boundary curve between the soft and hard switching regions for the upper switch can be determined by substituting (16) into (10). The previous expression can be used for the upper or lower switches of the input bridge when d = 0.5.

In order to achieve ZVS in the lower switches of the input bridges, it is necessary to define  $i_L(2\pi d) = 0$ . Applying this condition to (13) gives

$$\sin\left(2\cdot\pi\cdot d - \varphi\right) = 0. \tag{17}$$

The static gain expression for the boundary curve of the lower input switches is obtained by substituting (14) into (17) and rearranging the resulting equation as

$$G_{il} = \frac{V_i(d)}{2 \cdot V_i} \cdot \frac{A - B}{\cos \alpha + \sin \alpha \cdot \tan \left(2 \cdot \pi \cdot d\right)}$$

(18)

where

$$A = \cos \gamma \cdot [1 - \cos \theta - \sin \theta \cdot \tan (2 \cdot \pi \cdot d)] \qquad (19)$$

$$B = \sin \gamma \cdot \left[\sin \theta + (1 - \cos \theta) \cdot \tan \left(2 \cdot \pi \cdot d\right)\right]. \quad (20)$$

The power for the boundary curve between the soft and hard switching regions for the upper switch is found by substituting (18) into (10).

The third condition to achieve ZVS in the output bridges is to find the value of  $i_L(\alpha) = 0$ . Applying this condition to (13) gives

$$\sin\left(\alpha - \varphi\right) = 0. \tag{21}$$

The static gain expression for the boundary curve of the output bridge switches is obtained by substituting (14) into (21) and rearranging the resulting equation as

$$G_o = \frac{V_i(d)}{2 \cdot V_i} \cdot \frac{C - D}{\cos \alpha + \sin \alpha \cdot \tan \alpha}$$

(22)

where

$$C = \cos \gamma \cdot [1 - \cos \theta - \sin \theta \cdot \tan \alpha] \tag{23}$$

$$D = \sin \gamma \cdot \left[\sin \theta + (1 - \cos \theta) \cdot \tan \alpha\right].$$

(24)

Analogously to the case of the input bridge switching conditions, the power for the boundary curve of the output bridge switches is found substituting (22) into (10).

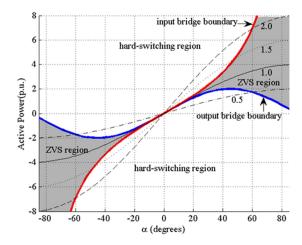

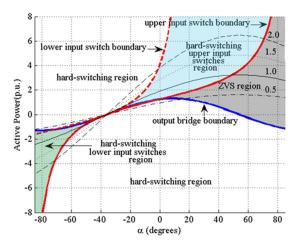

Fig. 7 are plotted substituting (16), (18) and (22) into (10) and varying static gain *G*, whose values are 0.5, 1.0, 1.5, and 2.0 in this case. It can be seen that, independently on the static gain, the ZVS region always lies between the boundaries, while the primary upper and lower switches boundaries behave similarly. For the remaining cases, only one bridge operates in ZVS mode. When  $\theta$  and *d* equal 180° and 0.5, respectively, also considering unity static gain, the converter operates in ZVS mode for any value of  $\alpha$ .

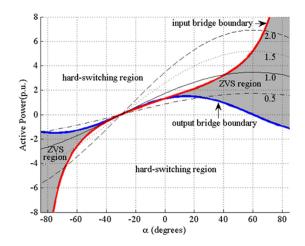

Fig. 8 presents the case where  $\theta$  is adjusted to 120°, as the ZVS region occurs between the boundary curves. Decreasing  $\theta$

Fig. 7. Input and output bridge soft-switching boundary for d=0.5 and  $\theta=180^\circ.$

Fig. 8. Input and output bridge soft-switching boundary curves for d = 0.5 and  $\theta = 120^{\circ}$ .

eliminates the ZVS characteristic for unity static gain at high values of  $\alpha$  (in this specific case, for  $\alpha > 40^{\circ}$ ).

When the duty cycle tends to extreme values (i.e., 0 or 1), the switching characteristics are modified. The analysis shown in Fig. 9 considers that the duty cycle is 0.3, while three regions exist. The first one is a ZVS region, which lies between the output bridge and the upper and lower input switch boundaries. In the second region, the hard-switching behavior only occurs in the upper input switches. The third region presents soft-switching for the output bridge and upper input switches. Finally, there is the fourth region, which is composed by the remaining parts, where hard-switching characteristics are similar to previous case with two regions, but they are inverted.

#### III. ANALYSIS OF THE ACTUAL MODEL

The previous session presented the analysis of power flow and switching characteristics considering the fundamental

Fig. 9. Input and output bridge soft-switching boundary for d=0.3 and  $\theta=180^\circ.$

Fig. 10. Simplified representation used in the analysis of the actual converter model analysis.

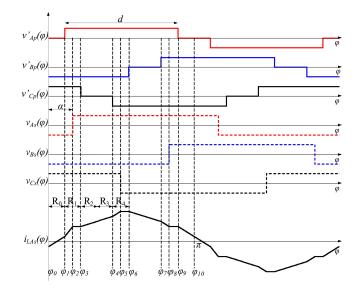

components of the voltages across the transformer. However, it is worth to check if the high-frequency harmonics due to the switches commutation can affect the aforementioned issues significantly. For this purpose, the actual model of the converter is presented and mathematically described as follows. The analysis is quite complex, which is composed of four (due to the variation of *d*) times four (due to the variation of  $\alpha$ ) regions in a total of 16 regions for a given direction of power flow and using a fixed value for  $\theta$ . That is why the derived analysis considers  $\theta = 180^{\circ}$  and a single region for the duty cycle.

#### A. Power Flow

The topology presented in Fig. 1 can be simplified in the form of the equivalent circuit in Fig. 10 where the primary side is referred to the secondary one, where  $L_{LA}$ ,  $L_{LB}$ , and  $L_{LC}$  are the leakage inductances per phase;  $V'_{Ap}$ ,  $V'_{Bp}$ ,  $V'_{Cp}$ , are the phase voltages across the primary side referred to secondary side;  $V_{As}$ ,  $V_{Bs}$ ,  $V_{Cs}$  are the voltages across the secondary winding with regard to the dc bus midpoint. According to the switching states, the duty cycle, and phase shift  $\alpha$ , the current through the transformer is supposed to assume a given shape and, consequently, a particular analysis for each case must be carried out. Therefore, the converter analysis must be performed according to the

Fig. 11. Primary voltage and current waveforms in the transformer and secondary voltage with regard to dc bus midpoint for 1/3 < d < 1/2 and  $(1-2d)\pi/2 < \alpha < \pi/3 - (1-2d)\pi/2$ .

existing operating regions, also considering the aforementioned current waveform.

Fig. 11 presents all waveforms that represent the operation of the equivalent circuit in Fig. 10, and also the current through the secondary side in phase A considering 1/3 < d < 1/2 and region R1, which corresponds to  $(1 - 2d)\pi/2 < \alpha < \pi/3 - (1 - 2d)\pi/2$ . The analysis considers that  $\alpha = 0$  occurs according to the fundamental component of the phase voltage  $v_{Ap}(\varphi)$ , where  $\varphi = \omega t$ . It can be stated that there are ten operating stages for a complete period of voltage  $v_{Ap}$ '( $\varphi$ ). Adopting terminals 1 and 2 as a reference, the Thèvenin equivalent circuit, and consequently the expressions that correspond to the voltage, current, and inductance can be determined as (25)–(27), respectively

$$V_{\rm th} = V'_{Ap} - GV_{As} - \frac{V'_{Bp} - GV_{Bs}}{2} - \frac{V'_{Cp} - GV_{Cs}}{2}$$

(25)

$$L_{\rm th} = \frac{L_L}{2} \tag{26}$$

$$i_{L_{As}}(\varphi) = \int \frac{2}{3} \cdot \frac{V_{\rm th}}{\omega L_L} d\varphi = i_{L_{As}}(\varphi_0) + \frac{2}{3} \cdot \frac{V_{\rm th}}{\omega L_L} (\varphi - \varphi_0).$$

(27)

In order to analyze the operating stages, it is necessary to define the average voltages. Considering  $V_o = V_{dco}/2$ , the voltage across the primary side may assume three levels  $(-V_o, 0, +V_o)$ , while that across the secondary one may assume two levels  $(-V_o, +V_o)$ . By employing (25) and (27) and determining the voltage level for each operating stage, the current can be

determined as

$$i_{L_{As}}(\varphi) = \begin{cases} i_{L_{As}}(\varphi_{0}) + \frac{2}{3} \frac{V_{o}G}{\omega L}(\varphi), \varphi_{0} \leq \varphi < \varphi_{1} \\ i_{L_{As}}(\varphi_{1}) + \frac{2}{3} \frac{V_{o}(1+G)}{\omega L}(\varphi - \varphi_{1}), \varphi_{1} \leq \varphi < \varphi_{2} \\ i_{L_{As}}(\varphi_{2}) + \frac{2}{3} \frac{V_{o}(1-G)}{\omega L}(\varphi - \varphi_{2}), \varphi_{2} \leq \varphi < \varphi_{3} \\ i_{L_{As}}(\varphi_{3}) + \frac{2}{3} \frac{V_{o}(2-G)}{\omega L}(\varphi - \varphi_{3}), \varphi_{3} \leq \varphi < \varphi_{4} \\ i_{L_{As}}(\varphi_{4}) + \frac{2}{3} \frac{V_{o}(2-2G)}{\omega L}(\varphi - \varphi_{4}), \varphi_{4} \leq \varphi < \varphi_{5} \\ i_{L_{As}}(\varphi_{5}) + \frac{2}{3} \frac{V_{o}(2-2G)}{\omega L}(\varphi - \varphi_{5}), \varphi_{5} \leq \varphi < \varphi_{6} \\ i_{L_{As}}(\varphi_{6}) + \frac{2}{3} \frac{V_{o}(2-2G)}{\omega L}(\varphi - \varphi_{5}), \varphi_{6} \leq \varphi < \varphi_{7} \\ i_{L_{As}}(\varphi_{7}) + \frac{2}{3} \frac{V_{o}(1-2G)}{\omega L}(\varphi - \varphi_{7}), \varphi_{7} \leq \varphi < \varphi_{8} \\ i_{L_{As}}(\varphi_{8}) + \frac{2}{3} \frac{V_{o}(1-G)}{\omega L}(\varphi - \varphi_{8}), \varphi_{8} \leq \varphi < \varphi_{9} \\ i_{L_{As}}(\varphi_{9}) + \frac{2}{3} \frac{V_{o}(-G)}{\omega L}(\varphi - \varphi_{9}), \varphi_{9} \leq \varphi < \varphi_{10} \end{cases}$$

$$(28)$$

where  $\varphi_{[0-10]}$  represents the instant between the operating stages. The instants can be found in (29).

Substituting (28) into (30) allows determining the expression for the output power in  $R_1$ , as the same procedure can be carried out for the remaining regions. The generic expression valid for regions  $R_1$  to  $R_4$  is represented by (31)

$$\begin{cases} \varphi_{0} = 0 \\ \varphi_{1} = (1 - 2d)\frac{\pi}{2} \\ \varphi_{2} = \alpha \\ \varphi_{3} = \frac{\pi}{3} - (1 - 2d)\frac{\pi}{2} \\ \varphi_{4} = \frac{\pi}{3} + (1 - 2d)\frac{\pi}{2} \\ \varphi_{5} = \frac{\pi}{3} + \alpha \\ \varphi_{6} = \frac{2\pi}{3} - (1 - 2d)\frac{\pi}{2} \\ \varphi_{7} = \frac{2\pi}{3} + (1 - 2d)\frac{\pi}{2} \\ \varphi_{8} = \frac{2\pi}{3} + \alpha \\ \varphi_{9} = \pi - (1 - 2d)\frac{\pi}{2} \\ \varphi_{10} = \pi \end{cases}$$

$$(29)$$

$$P_{o} = \frac{3}{2\pi} \int_{0}^{2\pi} G \cdot v_{As} (\varphi) \cdot i_{L_{As}} (\varphi) d\varphi \qquad (30)$$

$$P_{o} (\alpha, d) = \begin{cases} \frac{K_{P_{o}}}{3} \left[ 6\pi d (1-d) + 8\alpha - \frac{6\alpha^{2}}{\pi} - \frac{3\pi}{2} \right], \\ \varphi_{1} \le \alpha < \varphi_{3} \\ \frac{K_{P_{o}}}{3} \left[ \pi d (7-9d) + (7+6d) \alpha - \frac{9\alpha^{2}}{\pi} - \frac{19\pi}{12} \right] \\ \varphi_{3} \le \alpha < \frac{\pi}{3} \\ \frac{K_{P_{o}}}{3} \left[ \pi d (7-9d) + (7+6d) \alpha - \frac{9\alpha^{2}}{\pi} - \frac{19\pi}{12} \right] \\ \frac{\pi}{3} \le \alpha < \varphi_{4} \\ 4K_{P_{o}} \left[ \pi d (1-d) + \alpha - \frac{\alpha^{2}}{\pi} - \frac{11\pi}{36} \right] \\ \varphi_{4} \le \alpha < \varphi_{6} \end{cases}$$

$$(31)$$

where

$$K_{P_o} = \frac{GV_o^2}{\omega L}.$$

(32)

## B. Switching Characteristics

The conditions that allow achieving ZVS in the actual model for the upper and lower switches in the input bridge, and switches in the output bridge are  $i_{As}[(1-2d)\pi/2] = 0$ ,  $i_{As}[\pi - (1-2d)\pi/2] = 0$  and  $i_{As}(\alpha) = 0$ , respectively. If the aforementioned conditions are applied to the expression of the current valid for a given region, the boundary curves that define soft switching can be obtained. The expressions for the boundary curves of the upper side switch in the input bridge, lower switch of the input bridge, and switch of the output bridge are given by (33)–(35), respectively

$$G_{iu} = \begin{cases} -\frac{\pi (1+6d)}{6 (\alpha + \pi d) - 7\pi}, & \varphi_1 \le \alpha < \varphi_3 \\ -\frac{\pi (1+6d)}{6 (\alpha + \pi d) - 7\pi}, & \varphi_3 \le \alpha < \frac{\pi}{3} \\ -\frac{\pi (1+6d)}{6 (\alpha + \pi d) - 7\pi}, & \frac{\pi}{3} \le \alpha < \varphi_4 \\ -\frac{\pi (1+6d)}{12 [\alpha + \pi (d-1)]}, & \varphi_4 \le \alpha < \varphi_6 \end{cases}$$

(33)

$$G_{il} = \begin{cases} -\frac{\pi (1+6d)}{6 (\alpha - \pi d) - \pi}, & \varphi_1 \le \alpha < \varphi_3 \\ -\frac{\pi (1+6d)}{12 (\alpha - \pi d)}, & \varphi_3 \le \alpha < \frac{\pi}{3} \\ -\frac{\pi (1+6d)}{12 (\alpha - \pi d)}, & \frac{\pi}{3} \le \alpha < \varphi_4 \\ -\frac{\pi (1+6d)}{12 (\alpha - \pi d)}, & \varphi_4 \le \alpha < \varphi_6 \end{cases}$$

(34)

$$G_{o} = \begin{cases} \frac{2\pi - 3\alpha}{2\pi}, & \varphi_{1} \leq \alpha < \varphi_{3} \\ \frac{\pi (7 + 6d) - 18\alpha}{8\pi}, & \varphi_{3} \leq \alpha < \frac{\pi}{3} \\ \frac{\pi (7 + 6d) - 18\alpha}{8\pi}, & \frac{\pi}{3} \leq \alpha < \varphi_{4} \\ \frac{3\pi - 6\alpha}{2\pi}, & \varphi_{4} \leq \alpha < \varphi_{6}. \end{cases}$$

(35)

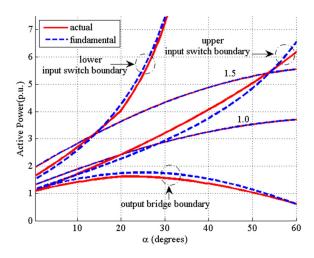

Fig. 12 compares the power and switching curves obtained from expressions (10), (16), (18), and (22) in the fundamental model and expressions (31)–(35) for the actual model. As the references for the fundamental model and actual model are different, the correction factor  $-(1 - 2d)\pi/2$  was added for variable  $\alpha$  in (31). It can be seen that the curves are nearly the same for G = 1.0 and G = 1.5. The boundary curves between the hard and soft commutation regions are plotted and compared with the ones obtained from the fundamental model. Satisfactory match is obtained considering the phase shift angle ranging from 0° to 60° and the duty cycle between 1/3 and 0.5. It is

Fig. 12. Input and output bridge soft-switching boundary curves for the actual and fundamental models for d = 0.389 and  $\theta = 180^{\circ}$ .

TABLE I SPECIFICATIONS FOR THE MODEL VALIDATION

| Input Voltage Vi   | 96 V      |

|--------------------|-----------|

| Output Voltage Vo  | 350-380 \ |

| Output Power $P_o$ | 3.5 kW    |

TABLE II Assumptions for the Model Validation

| Phase-shift angle $\alpha$                        | ±25°   |

|---------------------------------------------------|--------|

| Phase-shift angle $\theta$                        | 180°   |

| Duty cycle d                                      | 0.5    |

| Switching frequency $f_s$                         | 20 kHz |

| Dc input voltage ripple $\Delta V_{\mathrm{dc}i}$ | 5%     |

| Dc output voltage ripple $\Delta V_{ m dco}$      | 5%     |

|                                                   |        |

interesting to note that the maximum percentage error verified between the power curves for the actual model and the fundamental model is approximately 0.4% for G = 1.0 and 1.6% for G = 1.5. These excellent matches occur when d is equal to 0.389 (or varies from d = 1/2 until d = 1/3) as the current waveform  $i_{As}(\varphi)$  is nearly sinusoidal.

#### IV. EXPERIMENTAL RESULTS

The specifications and assumptions for the model validation are shown in Table I and II, respectively. The values chosen for  $\alpha$ ,  $\theta$ , d, and G are supposed to ensure that the converter presents soft-switching and high power factor. A reduced value of  $\alpha$  in association with  $\theta = 180^{\circ}$  provides low reactive power flow through the transformer, as observed in Figs. 4 and 6. When the duty cycle is 0.5 and the static gain is unity, ZVS occurs over the entire operation range, as observed in Fig. 7. Good tradeoffs can be obtained by choosing  $\alpha < 30^{\circ}$ .

Equations (10) and (12) are also used to obtain the leakage inductance, which is 22.16  $\mu$ H. The design of the transformer and inductor required to complement the leakage inductance is performed according to [32]. Therefore, the transformer turns

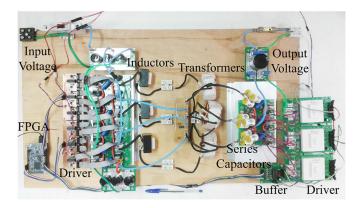

Fig. 13. Experimental prototype.

TABLE III Power Circuit Components used for the Model Validation

| Input electrolytic capacitor             | $6 \times 100 \ \mu$ F/400 V                                             |

|------------------------------------------|--------------------------------------------------------------------------|

| Input polypropylene capacitor            | $6 \times 1 \ \mu$ F/400 V                                               |

| Output electrolytic capacitor            | $1 \times 470 \ \mu$ F/450 V                                             |

| Output polypropylene capacitor           | $3 \times 470$ nF/630 V                                                  |

| Secondary polypropylene series capacitor | $3 \times 3 \mu$ F/100 V (per phase)                                     |

| Transformer                              | $3 \times \text{Core Magmattec MMT139T6325},$<br>n = 29/15               |

| Inductor                                 | $3 \times L_d = 21.5 \ \mu$ H, core Thornton NEE 42/21/20, $N_{Ld} = 15$ |

| Primary switches                         | $12 \times IRFP4321PbF$                                                  |

| Secondary switches                       | $6 \times IRGP50B60PD$                                                   |

ratio is n = 29/15 in this case. Besides, the ideal value of  $V_{dco} = 371.2$  V associated with unity static gain is obtained from (6).

Fig. 13 shows the experimental prototype and the power circuit components given in Table III, which are designed according to Table I and II. Some experimental results are presented and discussed as follows.

## A. Experimental Results for Model Validation

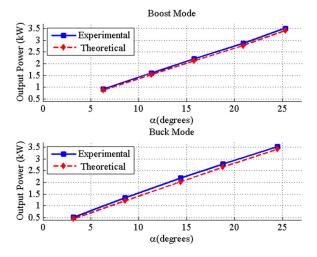

A comparison between experimental and theoretical (fundamental model) results is shown in Fig. 14. The initial and final errors in boost mode are 5.3% and 2.7%, respectively. The difference occurs due to the harmonic contents of the waveforms in the experimental prototype, which has not been considered in the fundamental model. Analogously, buck mode has presented initial and final errors of 13.6% and 2.9%, respectively.

#### B. Experimental Results for Rated Power

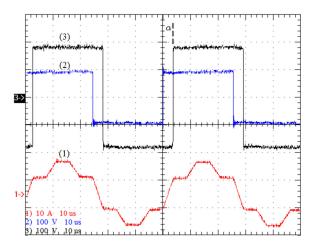

Fig. 15 shows the primary and secondary leg line voltages with regard to the dc bus midpoint and also the secondary current when the converter operates in boost mode. The maximum values for the voltages are primary and secondary voltages are 96 and 355.1 V, respectively. The output voltage was adjusted to ensure the best shape for the current through the transformer and, consequently, the maximum system efficiency. The difference between theoretical and experimental output voltages occurs due to semiconductors and magnetics stresses. The rms secondary line current is 7.8 A. The PS angle  $\alpha$  between primary

Fig. 14. Comparison between experimental and theoretical results for the operation in boost and buck modes.

Fig. 15. Secondary line current  $I_{LAs}$  (1–10 A/div; 10  $\mu$ s/div), primary line voltage  $V_{As}$  (2–100V/div; 10  $\mu$ s/div), and secondary line voltage (leg with regard to dc bus midpoint)  $V_{Ap}$  (3–100 V/div; 10  $\mu$ s/div).

and secondary sides can be seen according to the displacement between the voltage waveforms.

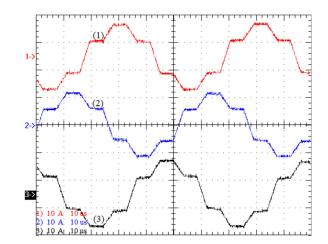

Three secondary line currents are shown in Fig. 16. The waveforms are symmetric and the existing dc component is less than 1%. Secondary line currents do not present dc components due to the use of series capacitors.

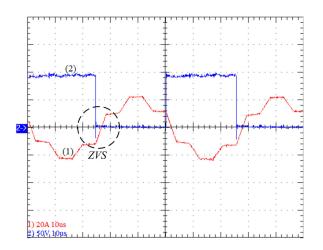

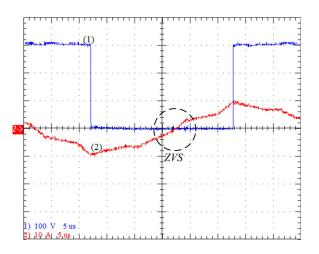

The switching profile for the design example is shown in Figs. 17 and 18. It is worth to mention that the currents through the switches are measured indirectly using the line currents considering that the converter operates in boost mode. The primary side is represented by Fig. 17 and secondary side corresponds to by Fig. 18. ZVS occurs in both cases, which is expected according to specifications in Table I and the profile presented in Fig. 7 for  $\alpha = 25.0^{\circ}$ .

# C. Switching Characterization for Static Gain Modified

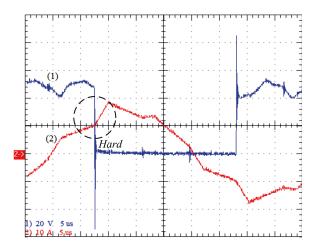

The waveforms shown in this section are obtained using a static gain, although ever the bus voltages are adjusted to half

Fig. 16. Secondary line currents  $I_{Ls}$  (1–10 A/div and 10  $\mu$ s/div; 2–10 A/div and 10  $\mu$ s/div; 3–10 A/div and 10  $\mu$ s/div).

Fig. 17. Primary switch current  $I_{LAp}$  (1–20 A/div;- 10  $\mu$ s/div) and primary switch voltage  $V_{SA1}$  (2–50 V/div; 10  $\mu$ s/div).

Fig. 18. Secondary switch current  $I_{LAs}$  (1–10 A/div– 10  $\mu$ s/div) and secondary switch voltage  $V_{S1}$  (2–100 V/div; 10  $\mu$ s/div).

Fig. 19. Results for  $\alpha = 20^{\circ}$  and G = 1.5: Primary switch voltage  $V_{SA1}$  (1–20 V/div; 5  $\mu$ s/div) and primary switch current  $I_{LAp}$  (2–10 A/div; 5  $\mu$ s/div).

Fig. 20. Results for  $\alpha = 20^{\circ}$  and G = 1.5: Secondary switch voltage  $V_{S1}$  (1–100 V/div; 5  $\mu$ s/div) and secondary switch current  $I_{LAs}$  (2–10 A/div; 5  $\mu$ s/div).

of the rated value, i.e.,  $V_{dc_i} = 48$  V and  $V_{dc_o} = 200$  V to avoid damaging the prototype.

According to Fig. 7, when  $\alpha = 20^{\circ}$  and the static gain equals 1.5 ( $V_{dc_o} = 300$  V), the input bridge presents hard switching. The experimental results presented in Figs. 19 and 20 validate this behavior. Besides, it is possible to observe an overvoltage across the switches and a high dc voltage ripple in the input bridge.

## D. Efficiency

Fig. 21 presents the measured efficiency of the converter as a function of the output power for the converter operating in boost and buck modes. The effective PS angles obtained for each measurement are shown, which are different from the applied values ( $5^{\circ}$ ,  $10^{\circ}$ ,  $15^{\circ}$ ,  $20^{\circ}$ , and  $25^{\circ}$ ) due to delays provided by drivers and buffers. Operation in boost mode provides an efficiency of 95.9% at rated power of 3500.6 W, while the maximum value is 96.7%. The efficiency in buck mode is slightly lower than

Fig. 21. Efficiency curves in boost and buck modes.

that in boost mode, i.e., 95.8% at rated power of 3520.0 W and maximum efficiency of 96.4%.

# V. CONCLUSION

This paper has presented the steady-state analysis of a ZVS bidirectional isolated three-phase dc–dc converter with DPS and variable duty cycle. According to the derived equations and graphs generated from the fundamental model analysis, it is possible to obtain the optimum design specifications that ensure high power factor at rated condition and soft-switching. Besides, the validation performed in Section V proves that both soft-switching conditions and the power curves can be obtained from the fundamental model.

The experimental results have validated the fundamental model, while the difference between theoretical and experimental efficiency curves is small. The converter efficiency is satisfactory, which is about 96% at rated power. The optimal result occurs due to phase parallelism in the primary side and soft-switching operation. Therefore, the proposed approach can be seen as an efficient solution for high-power applications considering the design guidelines given in the paper.

Future work includes an analysis of the dynamic model and a new control architecture considering the three control variables in order to perform power flow control optimizing the reactive contents and soft-switching conditions. Also, the control of the magnetizing current can be made to eliminate dc components through transformer current and, consequently, to eliminate the series capacitors.

#### REFERENCES

- D. S. Oliveira Jr. and I. Barbi, "A three-phase ZVS PWM DC-DC converter with asymmetrical duty cycle associated with a three-phase version of the hybridge rectifier," *IEEE Trans. Power Electron.*, vol. 20, no. 2, pp. 354–360, Mar. 2005.

- [2] A. R. Prasad, P. D. Ziogas, and S. Manias, "Analysis and design of a three-phase off-line dc-dc converter with high-frequency isolation," in *Proc. IEEE Ind. Appl. Soc. Annu. Meet.*, 1988, vol. 1, pp 813–820.

- [3] P A. R. Prasad, D. Ziogas, and S. Manias, "A three phase resonant PWM dc/dc converter," in *Proc. IEEE 22nd Annu. Power Electron. Spec. Conf.*, 1991, pp. 463–473.

- [4] A. K. S. Bhat, and R. L. Zheng, "A three-phase series-parallel resonant converter-analysis, design, simulation, and experimental results," *IEEE Trans. Ind. Appl.*, vol. 32, no. 4, pp. 951–960, Jul. 1996.

- [5] S. Akre, M. Egan, and M. J. Willers, "Practical design methodology for a new three-phase DC-DC fully resonant converter employing LCC-type tank circuit," in *Proc. IEE 8th Int. Conf. Power Electron. Variable Speed Drives*, 2000, pp 340–345.

- [6] S. Akre and M. Egan, "Analysis and design of a new three-phase resonant dc-dc converter with a capacitive output filter," in *Proc. IEEE 32nd Annu. Power Electron. Spec. Conf.*, 2001 vol. 1, pp 277–284.

- [7] D. S. Oliveira Jr. and I. Barbi, "A three-phase ZVS PWM dc-dc converter with asymmetrical duty cycle for high power applications," *IEEE Trans. Power Electron.*, vol. 20, no. 2, pp. 370–377, Mar. 2005.

- [8] D. S. Oliveira Jr., F. L. M. Antunes, and C. E. A. Silva, "A three-phase ZVS PWM DC–DC converter associated with a double-wye connected Rectifier, delta primary," *IEEE Trans. Power Electron.*, vol. 21, no. 6, pp. 354–360, Nov./Dec. 2006.

- [9] C. Liu, A. Johnson, and J. Lai, "A novel three-phase high-power softswitched dc-dc converter for low-voltage fuel cell applications," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1691–1697, Nov. 2005.

- [10] J. Choi, H. Cha, and B.M. Han, "A three-phase interleaved DC–DC converter with active clamp for fuel cells," *IEEE Trans. Power Electron.*, vol. 25, no. 8, pp. 2115–2123, Aug. 2010.

- [11] C. Yoon, J. Kim, and S. Choi, "Multiphase DC–DC converters using a boost-half-bridge cell for high-voltage and high-power applications," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 381–388, Feb. 2011.

- [12] R. L. Andersen and I. Barbi, "A ZVS-PWM three-phase current-fed pushpull DC–DC converter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 3, pp. 838–847, Mar. 2013.

- [13] P. Xuewei, U. R. Prasanna, and A. K. Rathore, "Magnetizing-inductanceassisted extended range soft-switching three-phase AC-link current-fed DC/DC converter for low DC voltage applications," *IEEE Trans. Power Electron.*, vol. 28, no. 7, pp. 3317–3328, Jul. 2013.

- [14] E. Agostini Jr. and I. Barbi, "Three-phase three-level PWM DC–DC converter," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1847–1856, Jul. 2011.

- [15] D. V. Ghodke, K. Chatterjee, and B. G. Fernandes, "Modified softswitched three-phase three-level DC–DC converter for high-power applications having extended duty cycle range," *IEEE Trans. Ind. Electron.*, vol. 59, no. 9, pp. 3362–3372, Sep. 2012.

- [16] F. Liu, Y Chen, G. Hu, and X. Ruan, "Modified three-phase three-level DC/DC converter with zero-voltage-switching characteristic-adopting asymmetrical duty cycle control," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6307–6318, Dec. 2014.

- [17] R. W. A. A. De Doncker, D. M. Divan, and M. H. K. Kheraluwala, "A three-phase soft-switched high-power-density DC-DC converter for highpower applications," *IEEE Trans. Ind. Appl.*, vol. 27, no. 1, pp. 63–73, Jan./Feb. 1991.

- [18] H. van Hoek, M. Neubert, and R. W. De Doncker, "Enhanced modulation strategy for a three-phase dual active bridge – boosting efficiency of an electric vehicle converter," *IEEE Power Electron.*, vol. 28, no. 12, pp. 5499–5507, Dec. 2013.

- [19] S. P Engel, N. Soltau, H. Stagge, and R. W. De Doncker, "Improved instantaneous current control for high-power three-phase dual-active bridge DC–DC converters," *IEEE Power Electron.*, vol. 29, no. 8, pp. 4067–4077, Aug. 2014.

- [20] Z. Wang and H. Li, "A soft switching three-phase current-fed bidirectional dc-dc converter with high efficiency over a wide input voltage range," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 669–684, Feb. 2012.

- [21] S. Bal, A. K. Rathore, and D. Srinivasan, "Modular snubberless bidirectional soft-switching current-fed dual 6-pack (CFD6P) DC/DC converter," *IEEE Trans. on Power Electron.*, vol. 30, no. 2, pp. 519–523, Feb. 2015.

- [22] P. Xuewei, A. K. Rathore, "Naturally clamped soft switching current fed three-phase bidirectional DC/DC converter," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 3316–3324, May 2015.

- [23] R. Mirzahosseini and F. Tahami, "Phase-shift three-phase bidirectional series resonant DC/DC converter," in *Proc. 37th Annu. Conf. IEEE Ind. Electron. Soc.*, 2011, pp. 1137–1143.

- [24] H. Cha, J. Choi, W. Kim, and Blasko, "A new bi-directional three-phase interleaved isolated converter with active clamp," in *Proc. Applied Power Electron. Conf. Expo.*, 2009, pp 1766–1772.

- [25] K. Jin and C. Liu, "A novel PWM high voltage conversion ratio bidirectional three-phase DC/DC converter with Y-Δ connected transformer," *IEEE Trans. Power Electron.*, to be published, 2015.

- [26] H. Bai and C. Mi, "Eliminate reactive power and increase system efficiency of isolated bidirectional dual-active-bridge dc-dc converters using novel dual-phase-shift control," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2905–2914, Nov. 2008.

- [27] B. Zhao, Q. Song, W. Liu, and Y. Sun, "Overview of dual-activebridge isolated bidirectional DC–DC converter for high-frequency-link power-conversion system," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4091–4106, Aug. 2014.

- [28] H. Xiao and S. Xie, "A ZVS bidirectional DC-DC converter with phaseshift plus PWM control scheme," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 813–824, Mar. 2008.

- [29] Z. Ding, C. Yang, Z. Zhang, C. Wang, and S. Xie, "A novel soft-swtching multiport bidirecional DC-DC converter for hybrid energy storage system," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1595–1609, Apr. 2014.

- [30] H. M. Oliveira Filho, D. S. Oliveira Jr., C. E. A. Silva, and F. L. Tofoli, "ZVS bidirectional isolated three-phase DC-DC converter with dual phase-shift and variable duty cycle," in *Proc. IIEE/IAS Int. Conf. Ind. Appl.*, 2012, pp 1–8.

- [31] H. M. Oliveira Filho, D. S. Oliveira Jr., and P. P. Praça, "Soft-switching bidirectional isolated three-phase dc-dc converter with dual phase-shift and variable duty cycle," in *Proc. Brazilian Power Electron. Conf.*, 2013, pp 129–134.

- [32] C.W. T. McLyman, *Transformer and Inductor Design Handbook*. New York, NY, USA: Marcel Dekker, 1988, ch. 3, 4, and 12.

Herminio Miguel de Oliveira Filho (S'15) was born in Taguatinga, Brazil, in 1983. He received the B.Sc. and M.Sc. degrees in electrical engineering from the Federal University of Ceará (UFC), Fortaleza, Brazil, in 2007 and 2010, respectively. He is currently working toward the D.Sc. degree in the Group of Power Processing and Control, UFC.

He is currently an Assistant Professor and a Researcher in the Electrical Energy Processing and Planning Group (GProPEE), University for the International Integration of the Afro-Brazilian Lusophony,

Acarape, Brazil. His interest interests include control applications in power electronics, microcontrolled systems, switched mode power supplies, dc–dc conversion, and renewable energy applications.

energy applications.

**Demercil de Souza Oliveira Jr.** (M'02–SM'13) was born in Santos, Brazil, in 1974. He received the B.Sc. and M.Sc. degrees in electrical engineering from the Federal University of Uberlândia, Uberlândia, Brazil, in 1999 and 2001, respectively, and the Dr. degree from the Federal University of Santa Catarina, Florianópolis, Brazil, in 2004.

He is currently a Researcher in the Group of Power Processing and Control, Federal University of Ceará, Fortaleza, Brazil. His interest interests include static power converters, soft commutation, and renewable

**Paulo Peixoto Praça** (M'10) was born in Fortaleza-CE, Brazil, in 1979. He received the B.Sc. degree from the University of Fortaleza, Fortaleza-CE, in 2003, the M.Sc. and the Ph.D. degrees from the Federal University of Ceará, Fortaleza-CE, 2006 and 2011, respectively.

He is currently a Researcher in the Group of Power Processing and Control and has been a Professor since 2009 in the Federal University of Ceará. His research interests include static power converters, soft commutation, and renewable energy applications.